티스토리 뷰

6.2 상보형 MOS(CMOS 기술) (COMPLEMENTARY MOS (CMOS) TECHNOLOGY

DWD85 2024. 1. 9. 20:226.2.0 상보형 MOS(CMOS 기술)

> MOSFET의 기본적인 공정 순서는 다음과 같다.

> Trend 영역 Etch - 산화막 CVD - CMP 평탄화 - 산화막 & Poly Si 증착 - Gate Photo Patterning - Source Drain IIP.

> 그림 6.3 (a)는 N Channel MOSFET 또는 NFET, NMOS라고 한다.

> NFET의 전도되는 채널이 전자로 구성되어 있어 N 형이라고 하며 PFET은 정공으로 되어있어 P 형 채널의 소자이다.

> 게이트와 드레인의 가해지는 전압은 Vg, Vd이며 0V와 공급전압 Vdd 사이의 범위를 갖는다.

> NFET의 Body는 0V가 걸리고 PFET의 Body는 Vdd에 연결되어 PN 접합은 항상 역전압으로 걸려서 전류가 흐르지 않는다.

> NFET과 PFET의 채널은 반대이기 때문에 Vg=Vdd일 때 NFET은 켜지고 PFET은 꺼진다.

> Vg=0V 일 때 PEFT은 켜지고 NFET은 꺼진다.

> 이러한 상보하는 성질을 활용한 CMOS 또는 상보형 MOS라고 부르는 저전력 회로를 설계할 수 있다.

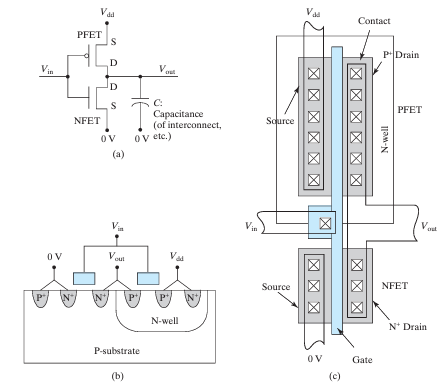

> 그림 6.4의 Inverter가 CMOS의 대표적인 예이다.

> 그림 6.4 (a)에서 Vg=Vdd 일 때 NFET은 켜지고 PFET 꺼지면서 출력단 Vout은 0V가 된다.

> Vg=0V일 때 NFET은 꺼지고 PFET은 켜지면서 출력단 Vout은 Vdd가 된다.

> Inverter가 작동 중 따라서 두 트랜지스터는 중 하나는 꺼지게 되면서 다른 종류 회로보다 더 적은 전력을 소모한다.

> CMOS를 형성하기 위해선 Body가 N, P형 두 가지 형태여야 한다.

> 이를 위해서 그림 6.4 (b) 처럼 P-sub에 N type 도핑을 해줘서 N-Well을 만들어주면 된다.

> 그림 6.4 (c)는 CMOS의 Layout이며 Vin, Vout, Vdd는 금속 선으로 연결된다.

> PFET이 NFET 보다 긴 이유는 PFET의 Mobility가 느리기 때문에 NFET의 Mobility와 맞춰주기 위함이다.

Reference

-. Chenming Calvin Hu, Modern Semiconductor Devices for Integrated Circuits, PEARSON(2013)

'Semiconductor(반도체)' 카테고리의 다른 글

| 6.3 표면 이동도와 고이동도 FET (Surface Mobilities and High-Mobility FETs) (2) (0) | 2024.01.15 |

|---|---|

| 6.3 표면 이동도와 고이동도 FET (Surface Mobilities and High-Mobility FETs) (1) (1) | 2024.01.14 |

| 6.1 MOSFET 소개 (Introduction to the MOSFET) (1) | 2024.01.08 |

| 5.10 CCD 및 CMOS 화상기 (CCD and CMOS Image Sensor) (0) | 2024.01.07 |

| 5.9 반전 및 축적 전하층 두께(Oxide Thickness Under Inversion and Accumulation Condition) (1) | 2023.12.12 |

- Total

- Today

- Yesterday

- Semicondcutor

- Charge Accumulation

- Reverse Bias

- MOS

- Donor

- Fiber Optic

- pn 접합

- Solar cell

- semiconductor

- Depletion Layer

- PN Junction

- 반도체

- Thermal Noise

- 양자 웰

- 쇼트키

- Acceptor

- Pinch Off

- C언어 #C Programming

- 광 흡수

- 문턱 전압

- 열전자 방출

- CD

- Blu-ray

- EBD

- Optic Fiber

- channeling

- Energy band diagram

- fermi level

- Diode

- Laser

| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | ||||

| 4 | 5 | 6 | 7 | 8 | 9 | 10 |

| 11 | 12 | 13 | 14 | 15 | 16 | 17 |

| 18 | 19 | 20 | 21 | 22 | 23 | 24 |

| 25 | 26 | 27 | 28 | 29 | 30 | 31 |