티스토리 뷰

6.11.0 직렬 저항과 유효 채널 길이의 추출

> Transistor의 Gate 길이 Lg는 실제 공정에서 만든 것과 Layout에서 설계한 길이 Ldrawn와 다르다.

> Patterning 과정에서 길이의 변화가 있으며 이 차이를 최소화 하는 OPC(Optical Proximity Correction)과 같은 기술이 도입된다.

> 하지만 차이를 완전한 0으로 만들기는 어려운 부분이 있고 소자를 해석할 때 유효 채널 길이 Leff를 도입하였다.

> Ldrawn - Lg 차이를 △L 이라고 하고 이 △L을 측정하는 방법은 아래 관계식으로 구할 수 있다.

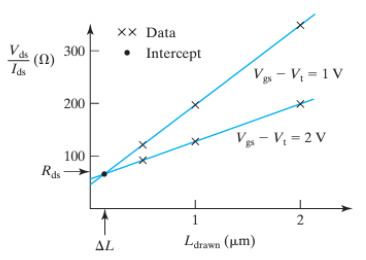

> Ldrawn만 다른 세개의 다른 MOSFET을 Ldrawn vs. Vds/Ids 그래프를 그리면 다음과 같다.

> Vds/Ids는 Ldrawn의 선형 함수이고 Vgs-Vt와 무관한 점에서 만나는데 이 점의 R은 Rds, L은 △L이다.

> 이렇게 구한 △L으로 실제 L을 구할 수 있다.

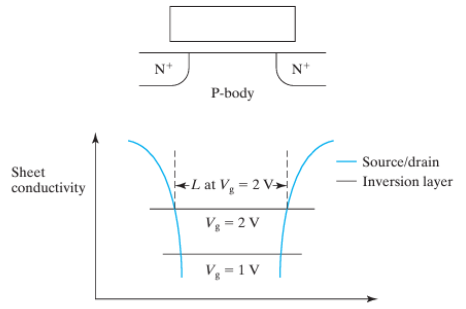

> Vg-Vt가 증가함에 따라 △L이 감소 (L이 증가) 한다.

> △L와 Rds가 Vg에 따라서 달라지는 점을 고려해서 Leff 해석해야 한다.

> MOSFET 채널은 Vg가 커짐에 따라 확장하고 도전율이 커진다.

> Vg가 커질수록 채널에 대한 Source/Drain에서 더 확산되어 Rds가 줄어든다.

Reference

-. Chenming Calvin Hu, Modern Semiconductor Devices for Integrated Circuits, PEARSON(2013)

'Semiconductor(반도체)' 카테고리의 다른 글

| 6.13 출력 컨덕턴스 (0) | 2024.05.28 |

|---|---|

| 6.12 속도 오버슛과 소오스 속도 한계 (1) | 2024.05.27 |

| 6.10 기생 소오스-드레인 저항 (0) | 2024.05.22 |

| 6.9 속도 포화 현상이 있을 경우의 MOSFET IV 모델 (0) | 2024.05.20 |

| 6.8 속도 포화 (Velocity Saturation) (0) | 2024.05.06 |

- Total

- Today

- Yesterday

- Depletion Layer

- Semicondcutor

- Diode

- Energy band diagram

- fermi level

- C언어 #C Programming

- 반도체

- Pinch Off

- MOS

- 양자 웰

- Solar cell

- Optic Fiber

- EBD

- Donor

- semiconductor

- PN Junction

- Thermal Noise

- Laser

- 광 흡수

- Reverse Bias

- Charge Accumulation

- channeling

- 문턱 전압

- 쇼트키

- Acceptor

- pn 접합

- Fiber Optic

- Blu-ray

- CD

- 열전자 방출

| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | ||

| 6 | 7 | 8 | 9 | 10 | 11 | 12 |

| 13 | 14 | 15 | 16 | 17 | 18 | 19 |

| 20 | 21 | 22 | 23 | 24 | 25 | 26 |

| 27 | 28 | 29 | 30 |