티스토리 뷰

5.4 문턱 조건 및 문턱 전압

> Gate 전압을 공핍 전압보다 더 증가하면 Gate 쪽 밴드 다이어그램은 더 내려간다.

> 특정한 Gate 전압에 도달하면 Si-SiO2 계면에서 Ef가 Ec와 충분히 가까워져 포면은 공핍에서 반전 조건에 도달한다.

> 반전이란 P형에서 N형으로 즉, 표면에 전자의 수가 매우 많은 상태로 바뀐 것이다.

> 이 전압 조건을 문턱 전압이라고 하고 표면에서 전자의 농도와 Bulk에서 도핑 농도 Na와 같아진다.

> 따라서 A = B이고 C = D 이다. (그림 1 참고)

> Ei는 밴드 갭 중간 즉, Ec와 Ev의 중간 부근에 그려진다.

> 문턱 조건에서 밴드가 휘는 정도를 ∅_st라고 하고 Nc=Nv라고 가정하면 ∅_st에 대한 식을 얻을 수 있다.

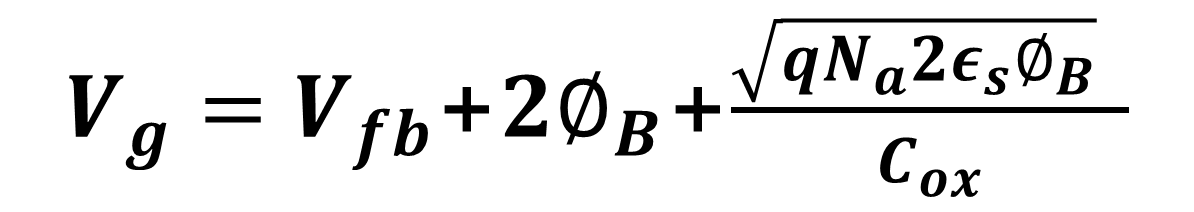

> 문턱 전압 기준으로 Gate 전압에 대한 식으로 표현하면 다음과 같다.

Reference

-. Chenming Calvin Hu, Modern Semiconductor Devices for Integrated Circuits, PEARSON(2013)

반응형

'Semiconductor(반도체)' 카테고리의 다른 글

| 5.6 MOS 커패시터의 C-V 특성(C-V Characteristics of MOS Capacitor) (0) | 2023.12.09 |

|---|---|

| 5.5 문턱 조건 이후 강반전(Strong Inversion) (1) | 2023.12.05 |

| 5.3 표면 공립(Surface Depletion) (1) | 2023.12.03 |

| 5.2 표면 축적(Surface Accumulation) (0) | 2023.12.02 |

| 5.1 평탄 밴드 조건과 평탄 밴드 전압(Flat Band Condition) (0) | 2023.12.01 |

반응형

공지사항

최근에 올라온 글

최근에 달린 댓글

- Total

- Today

- Yesterday

링크

TAG

- Charge Accumulation

- C언어 #C Programming

- Reverse Bias

- EBD

- Diode

- MOS

- Depletion Layer

- Solar cell

- Fiber Optic

- 반도체

- 문턱 전압

- fermi level

- 열전자 방출

- CD

- Donor

- pn 접합

- Optic Fiber

- Laser

- 양자 웰

- Pinch Off

- Acceptor

- PN Junction

- semiconductor

- Thermal Noise

- Energy band diagram

- Blu-ray

- Semicondcutor

- channeling

- 광 흡수

- 쇼트키

| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | 6 | 7 |

| 8 | 9 | 10 | 11 | 12 | 13 | 14 |

| 15 | 16 | 17 | 18 | 19 | 20 | 21 |

| 22 | 23 | 24 | 25 | 26 | 27 | 28 |

| 29 | 30 |

글 보관함